電子元器件是現(xiàn)代電子系統(tǒng)的基石,其設(shè)計水平直接決定了電子設(shè)備的性能、可靠性和成本。電子元器件的設(shè)計是一個融合了材料科學(xué)、半導(dǎo)體物理、微電子學(xué)、電路理論和先進(jìn)制造技術(shù)的復(fù)雜系統(tǒng)工程。本文將系統(tǒng)闡述電子元器件設(shè)計的基本流程、核心考量以及前沿趨勢。

一、 設(shè)計流程:從概念到產(chǎn)品

1. 需求分析與規(guī)格定義:這是設(shè)計的起點(diǎn)。設(shè)計師需要明確元器件的電氣特性(如工作電壓、電流、頻率、功率)、物理參數(shù)(尺寸、封裝)、環(huán)境適應(yīng)性(溫度、濕度、抗震)以及成本目標(biāo)。例如,設(shè)計一個用于手機(jī)電源管理的MOSFET,與設(shè)計一個用于工業(yè)電機(jī)驅(qū)動的IGBT,其規(guī)格要求截然不同。

2. 材料選擇與工藝規(guī)劃:根據(jù)規(guī)格要求,選擇合適的基底材料(如硅、砷化鎵、氮化鎵、碳化硅)、介質(zhì)材料和導(dǎo)體材料。確定制造工藝路線,如平面工藝、MEMS工藝或新興的3D集成工藝。材料與工藝的選擇深刻影響器件的性能極限和制造成本。

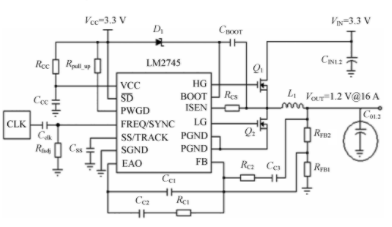

3. 結(jié)構(gòu)與版圖設(shè)計:這是設(shè)計的核心環(huán)節(jié)。利用計算機(jī)輔助設(shè)計(CAD)工具,進(jìn)行器件的物理結(jié)構(gòu)建模和電氣建模。例如,設(shè)計一個晶體管,需要精確設(shè)計其源極、漏極、柵極的幾何形狀、摻雜剖面以及絕緣層厚度。版圖設(shè)計則將這些結(jié)構(gòu)轉(zhuǎn)化為可供光刻使用的掩模圖形,需嚴(yán)格遵守設(shè)計規(guī)則以確保可制造性。

4. 仿真與驗(yàn)證:在投入昂貴流片之前,必須通過TCAD(工藝計算機(jī)輔助設(shè)計)、SPICE等仿真工具,對器件的電學(xué)特性、熱學(xué)特性乃至可靠性進(jìn)行模擬分析。仿真可以預(yù)測其I-V特性、開關(guān)速度、噪聲、功耗等關(guān)鍵指標(biāo),并進(jìn)行優(yōu)化迭代。

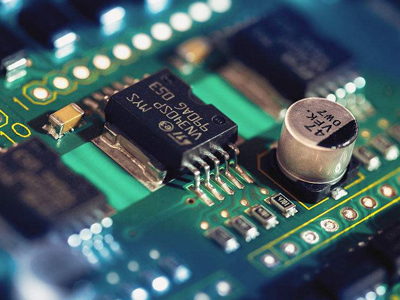

5. 原型制造與測試:通過流片制造出原型樣品,隨后進(jìn)行嚴(yán)格的實(shí)驗(yàn)室測試,包括直流參數(shù)測試、交流參數(shù)測試、可靠性測試(如HTOL、ESD)等,將實(shí)測數(shù)據(jù)與仿真結(jié)果對比,驗(yàn)證設(shè)計并發(fā)現(xiàn)問題。

6. 設(shè)計迭代與定型:根據(jù)測試反饋,修改設(shè)計并重復(fù)仿真、制造、測試循環(huán),直至滿足所有規(guī)格要求,最終完成設(shè)計定型并交付量產(chǎn)。

二、 設(shè)計的核心考量因素

1. 性能與功耗的平衡:尤其在移動計算和物聯(lián)網(wǎng)時代,如何在提升速度、驅(qū)動能力的降低靜態(tài)和動態(tài)功耗,是設(shè)計的永恒主題。這涉及到低功耗電路架構(gòu)、高遷移率新材料、先進(jìn)電源管理技術(shù)的應(yīng)用。

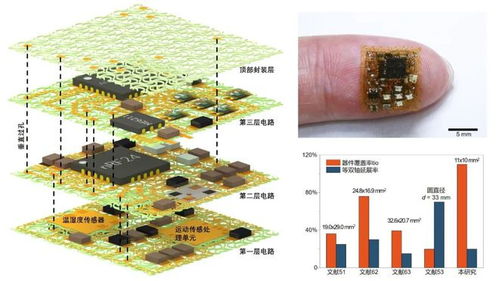

2. 集成度與微型化:遵循摩爾定律,器件特征尺寸不斷縮小,系統(tǒng)級封裝(SiP)和芯片級封裝(CSP)技術(shù)使得單個封裝內(nèi)能集成更多功能。設(shè)計需解決隨之而來的寄生效應(yīng)、信號完整性、散熱等挑戰(zhàn)。

3. 可靠性與魯棒性:元器件必須在規(guī)定的壽命內(nèi)穩(wěn)定工作。設(shè)計時必須考慮抗靜電放電(ESD)能力、抗閂鎖效應(yīng)(Latch-up)、熱載流子注入、電遷移以及長期工作下的老化機(jī)制,并通過設(shè)計加固手段提升魯棒性。

4. 成本與可制造性:優(yōu)秀的設(shè)計必須具有高的良率和可制造性。設(shè)計需要與工藝能力緊密配合,避免過于復(fù)雜或逼近工藝極限的結(jié)構(gòu),以控制制造成本。設(shè)計-for-制造(DFM)和設(shè)計-for-測試(DFT)理念貫穿始終。

三、 前沿趨勢與挑戰(zhàn)

1. 超越硅基:寬禁帶半導(dǎo)體:以氮化鎵(GaN)和碳化硅(SiC)為代表的第三代半導(dǎo)體,因其高擊穿場強(qiáng)、高電子飽和速率和優(yōu)異的熱性能,正革命性地推動功率器件和射頻器件的發(fā)展,設(shè)計方法需適應(yīng)新材料的特性。

2. More than Moore:異構(gòu)集成:在平面縮放逼近物理極限的背景下,通過2.5D/3D堆疊、芯粒(Chiplet)技術(shù),將不同工藝節(jié)點(diǎn)、不同功能的芯片(如邏輯、存儲、模擬、傳感器)集成在一起,這對互連設(shè)計、熱管理和測試提出了全新的設(shè)計要求。

3. 智能化與EDA工具演進(jìn):人工智能和機(jī)器學(xué)習(xí)正在賦能EDA工具,用于自動化布局布線、優(yōu)化設(shè)計參數(shù)、預(yù)測性能與良率,甚至進(jìn)行逆向設(shè)計,極大提升設(shè)計效率和探索新設(shè)計空間的能力。

4. 面向特定領(lǐng)域的設(shè)計:隨著AI、自動駕駛、量子計算等新興領(lǐng)域崛起,催生了對存算一體器件、毫米波/太赫茲器件、單光子探測器、量子比特等特種元器件的需求,其設(shè)計理論和方法往往需要顛覆性創(chuàng)新。

電子元器件的設(shè)計是一個持續(xù)演進(jìn)、多學(xué)科交叉的尖端領(lǐng)域。它不僅要求設(shè)計師具備扎實(shí)的理論基礎(chǔ),還需緊跟工藝進(jìn)步與應(yīng)用需求,在性能、功耗、面積、成本和可靠性等多重約束下尋求最優(yōu)解,從而為信息社會的每一次飛躍奠定硬件基礎(chǔ)。